Где именно L1, L2 и L3 кэши расположены в компьютере?

Где именно L1, L2 и L3 кэши расположены в компьютере?

Я знаю, что мы используем Cache для повышения производительности, выбирая DATA и INSTRUCTIONS из Cache, а не из основной памяти.

Ниже приведены мои вопросы

- Где именно находится L1 Cache?, находится на чипе процессора?

Где именно находится L2 Cache?

Где именно находится L3 Cache? находится на материнской плате?

Я думаю, что последние процессоры SMP используют 3-уровневые кэши, поэтому я хочу понять иерархию уровней кэша и их архитектуру.

6 ответов

Начнем с этого:

Я думаю, что последние процессоры SMP используют 3-уровневые кэши, поэтому я хочу понять иерархию уровней кэша и их архитектуру.

Чтобы понять кеши, вам нужно знать несколько вещей:

Процессор имеет регистры. Значения в этом могут быть непосредственно использованы. Нет ничего быстрее.

Однако мы не можем добавлять бесконечные регистры в чип. Эти вещи занимают место. Если мы сделаем чип больше, он станет дороже. Частично это связано с тем, что нам нужен чип большего размера (больше кремния), а также потому, что количество проблемных чипов увеличивается.

(Представьте себе воображаемую пластину размером 500 см 2. Я нарезал из нее 10 фишек, каждая из которых имеет размер 50 см 2. Одна из них сломана. Я выбрасываю ее и оставляю ей 9 рабочих фишек. Теперь возьмите ту же пластину и нарежу 100 чипов от него, каждый в десять раз меньше. Один из них сломан. Я выбрасываю сломанный чип, и у меня остается 99 рабочих чипов. Это часть потерь, которые я бы иначе получил. Чтобы компенсировать большее чипсы мне нужно было бы спросить более высокие цены. Больше, чем просто цена на дополнительный кремний)

Это одна из причин, почему нам нужны маленькие, доступные по цене чипы.

Однако чем ближе кэш-память к процессору, тем быстрее он может быть доступен.

Это также легко объяснить; Электрические сигналы распространяются со скоростью, близкой к скорости света. Это быстро, но все же конечная скорость. Современный процессор работает с тактовой частотой ГГц. Это тоже быстро. Если я возьму процессор 4 ГГц, то электрический сигнал может проходить около 7,5 см за такт. Это 7,5 см по прямой. (Чипсы - это не прямое соединение). На практике вам понадобится значительно меньше этих 7,5 см, поскольку это не дает чипам времени для представления запрошенных данных и возврата сигнала.

Суть в том, что мы хотим, чтобы кэш был максимально приближен к физическому. Что означает большие фишки.

Эти два должны быть сбалансированы (производительность против стоимости).

Где именно кэш-память L1, L2 и L3 находится в компьютере?

Предполагается, что стиль ПК только аппаратный (мэйнфреймы довольно разные, в том числе в соотношении производительности и стоимости);

IBM XT

Оригинальный 4.77Mhz один: нет кеша. Процессор обращается к памяти напрямую. Чтение из памяти будет следовать этой схеме:

- Процессор помещает адрес, который он хочет прочитать, на шину памяти и устанавливает флаг чтения.

- Память помещает данные на шину данных.

- ЦП копирует данные с шины данных во свои внутренние регистры.

80286 (1982)

Все еще нет кеша. Доступ к памяти не был большой проблемой для низкоскоростных версий (6 МГц), но более быстрая модель работала до 20 МГц и часто требовала задержки при доступе к памяти.

Затем вы получите такой сценарий:

- Процессор помещает адрес, который он хочет прочитать, на шину памяти и устанавливает флаг чтения.

- Память начинает помещать данные на шину данных. Процессор ждет.

- Память закончила получать данные, и теперь она стабильна на шине данных.

- ЦП копирует данные с шины данных во свои внутренние регистры.

Это дополнительный шаг в ожидании памяти. На современной системе это легко может быть 12 шагов, поэтому у нас есть кэш.

80386: (1985)

Процессоры становятся быстрее. Как за такт, так и на более высоких тактовых частотах.

Оперативная память становится быстрее, но не так быстро, как процессоры.

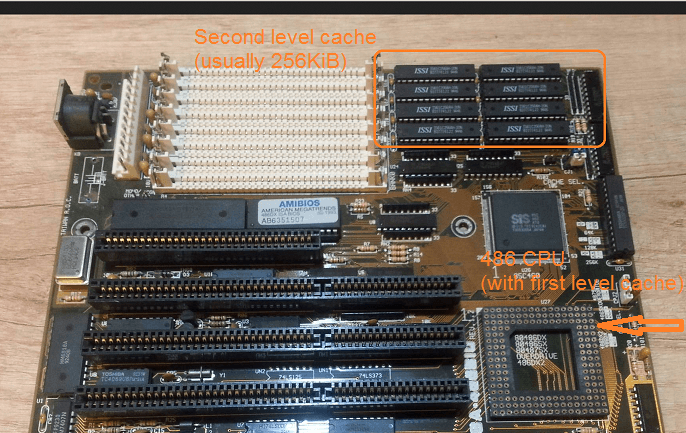

В результате требуется больше состояний ожидания. Некоторые материнские платы решают эту проблему, добавляя кеш (это был бы кеш первого уровня) на материнскую плату.

Чтение из памяти теперь начинается с проверки того, что данные уже находятся в кеше. Если это так, он читается из гораздо более быстрого кэша. Если не та же процедура, что описана с 80286

80486: (1989)

Это первый процессор этого поколения, который имеет некоторый кэш на процессоре.

Это унифицированный кеш объемом 8 КБ, что означает, что он используется для данных и инструкций.

Примерно в это же время принято ставить 256 КБ быстрой статической памяти на материнскую плату в качестве кэша 2- го уровня. Таким образом, кэш 1- го уровня на процессоре, кэш 2- го уровня на материнской плате.

80586 (1993)

586 или Pentium-1 использует разделенный кеш уровня 1. 8 КБ каждый для данных и инструкций. Кэш был разделен таким образом, чтобы кэши данных и инструкций можно было индивидуально настроить для их конкретного использования. У вас все еще есть небольшой, но очень быстрый 1- й кэш рядом с процессором, и более крупный, но более медленный 2- й кэш на материнской плате. (На большем физическом расстоянии).

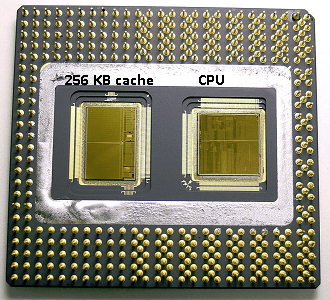

В той же области Pentium 1 Intel выпустила Pentium Pro ('80686'). В зависимости от модели этот чип имел 256 КБ, 512 КБ или 1 МБ кэш-памяти. Это было также намного дороже, что легко объяснить с помощью следующей картины.

Обратите внимание, что половина места в чипе используется кешем. И это для модели 256 КБ. Технически возможно увеличить объем кэша, а некоторые модели выпускаются с 512 КБ и 1 МБ кэшей. Рыночная цена на них была высокой.

Также обратите внимание, что этот чип содержит две матрицы. Один с реальным процессором и 1- м кешем, а второй - с 256-Кбайтным 2- м кешем.

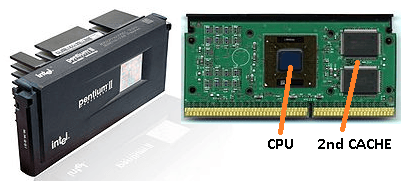

Pentium-2

Pentium 2 является ядром Pentium Pro. По соображениям экономии, второй процессор не находится в процессоре. Вместо того, что продается как процессор, мы используем печатную плату с отдельными чипами для процессора (и 1- го кеша) и 2- го кеша.

По мере развития технологии, и мы начинаем создавать чипы с более мелкими компонентами, становится финансово возможным вернуть второй кэш обратно в реальный процессор. Однако есть еще раскол. Очень быстрый 1- й кеш прижался к процессору. С одним 1- м кешем на ядро ЦП и большим, но менее быстрым 2- м кешем рядом с ядром.

Pentium-3

Pentium-4

Это не изменится для Pentium-3 или Pentium-4.

Примерно в это же время мы достигли практического предела того, как быстро мы можем синхронизировать процессоры. 8086 или 80286 не нуждались в охлаждении. Pentium-4, работающий на частоте 3,0 ГГц, вырабатывает столько тепла и потребляет столько энергии, что становится более практичным размещать два отдельных процессора на материнской плате, а не один быстрый.

(Два процессора с тактовой частотой 2,0 ГГц потребляют меньше энергии, чем один идентичный процессор с тактовой частотой 3,0 ГГц, но могут выполнять больше работы).

Это можно решить тремя способами:

- Сделайте процессоры более эффективными, чтобы они работали с той же скоростью.

- Используйте несколько процессоров

- Используйте несколько процессоров в одном и том же "чипе".

1) Это непрерывный процесс. Это не ново, и это не остановит.

2) Это было сделано раньше (например, с двумя материнскими платами Pentium-1 и чипсетом NX). До сих пор это был единственный вариант для создания более быстрого ПК.

3) Требуются процессоры, в которых несколько процессорных ядер объединены в одном чипе. (Затем мы назвали этот процессор двухъядерным процессором, чтобы увеличить путаницу. Спасибо, маркетинг:))

В наши дни мы просто называем процессор "ядром", чтобы избежать путаницы.

Теперь вы получаете такие чипы, как Pentium-D (Duo), который в основном состоит из двух ядер Pentium-4 на одном чипе.

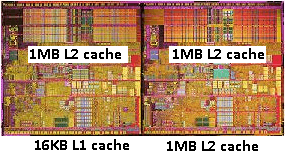

Помните фотографию старого Pentium-Pro? С огромным размером кеша?

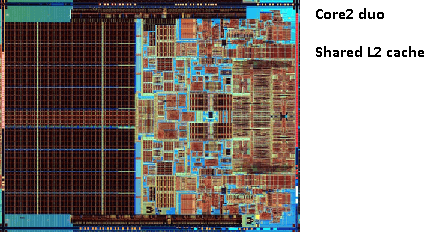

Видите две большие области на этой картинке?

Оказывается, мы можем разделить этот второй кеш между обоими ядрами процессора. Скорость может немного снизиться, но общий 2- й кэш 512 КБ часто быстрее, чем добавление двух независимых кешей 2- го уровня в два раза меньше.

Это важно для вашего вопроса.

It means that if you read something from one CPU core and later try to read it from another core which shares the same cache that you will get a cache hit. Memory will not need to be accessed.

Since programs do migrate between CPU's, depending on the load, the number of core and the scheduler you can gain additional performance by pinning programs which use the same data to the same CPU (cache hits on L1 and lower) or on the same CPUs which share L2 cache (and thus get misses on L1, but hits on L2 cache reads).

Thus on later models you will see shared level 2 caches.

If you are programming for modern CPUs then you have two options:

- Не беспокойся. The OS should be able to schedule things. The scheduler has a large impact on the performance of the computer and people have spent a lot of effort in optimising this. Unless you do something weird or are optimising for one specific model of PC you are better off with the default scheduler.

- If you need every last bit of performance and faster hardware is not an option, then try to leave the treads which access the same data on the same core or on a core with access to a shared cache.

I realise that I have not yet mentioned L3 cache, but they are not different. A L3 cache works in the same way. Bigger than L2, slower than L2. And it is often shared between cores. If it is present is is a lot bigger than the L2 cache (else having it would not make sense) and it is often shared with all cores.

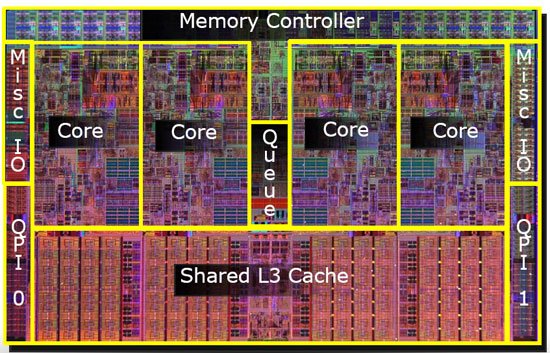

То, что кеши являются внутренностями процессора. Некоторые разделены между ядрами, некоторые индивидуальны, зависит от реализации. Но все они расположены на чипе. Некоторые детали: Процессор Intel Intel® Core™ i7, взятый здесь:

- 32-килобайтная инструкция и 32-килобайтный кэш первого уровня данных (L1) для каждого ядра

- Общий кэш второго уровня (256 КБ) для инструкций и данных (L2) для каждого ядра

- 8-МБ общий кэш инструкций / данных последнего уровня (L3), общий для всех ядер

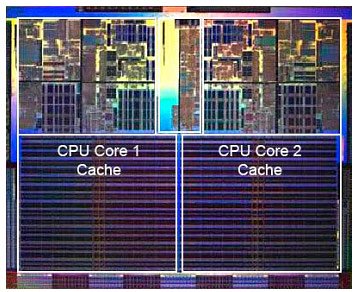

Фото чипа процессора (извините, не знаю точную модель). Вы можете видеть, что кэш занимает значительную площадь на чипе:

Кэш почти всегда находится на чипе для быстрого доступа. Вот хорошая диаграмма, показывающая четырехъядерный процессор Intel с выделенным кешем L3. Когда вы смотрите на подобные изображения кристалла ЦП, большие однородные области обычно представляют собой банки встроенной памяти, используемые в качестве кэша.

В эти дни все кэши на процессоре умирают. Раньше они иногда располагались на материнской плате или на дочерней плате ЦП, но я не думаю, что есть какие-то современные процессоры, которые используют кэш-память вне чипа.

Я не уверен насчет L3, но L1/L2 всегда находится на процессоре. С точки зрения иерархии, в основном, L1 обычно является кешем команд, L2 и L3 являются кешами данных.

L1 расположен на микросхеме ЦП, L2 расположен между процессором и основной памятью, но есть смысл знать, что в некоторых системах L2 находится на микросхеме ЦП, в то время как в некоторых других системах L2 находится на самой материнской плате, а L3 постоянно находится на основной плате чипа.